## EGC220 Class Notes 4/4/2023

## Baback Izadi

Division of Engineering Programs bai@engr.newpaltz.edu

## 1. Using Verilog, design an ALU with the following specification:

|   | S | Function |

|---|---|----------|

|   | 0 | A-B      |

|   | 1 | A+B      |

|   | 2 | A + 1    |

|   | 3 | A - 1    |

| / | 4 | A AND B  |

|   | 5 | A OR B   |

|   | 6 | A XOR B  |

|   | 7 | A'       |

```

module alu(s, A, B, F);

input [2:0] s;

input [3<mark>:</mark>0] A, B;

output [3:0] F;

reg [3|:0] F;

always @(s or A or B)

case (s)

0: F = A - B;

1: F = A + B;

2: F = A + 1;

3: F = A - 1;

7: F = \sim A;

4: F = A \& B;

endcase

5: F = A \mid B;

endmodule

6: F = A \wedge B;

```

Problem 2

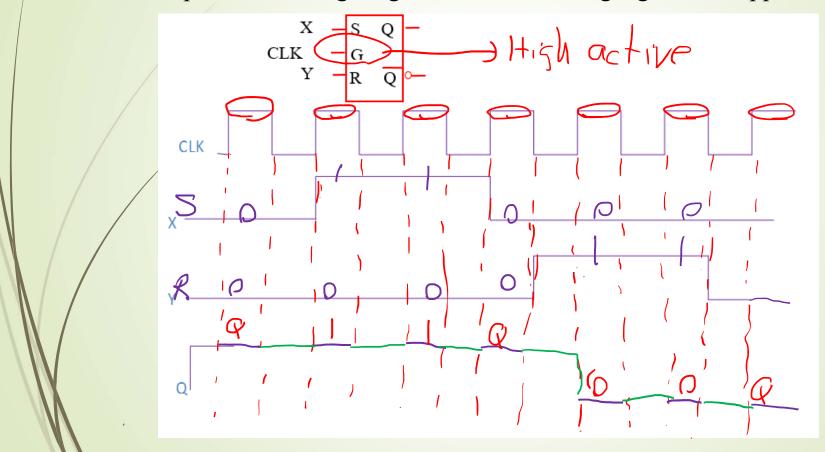

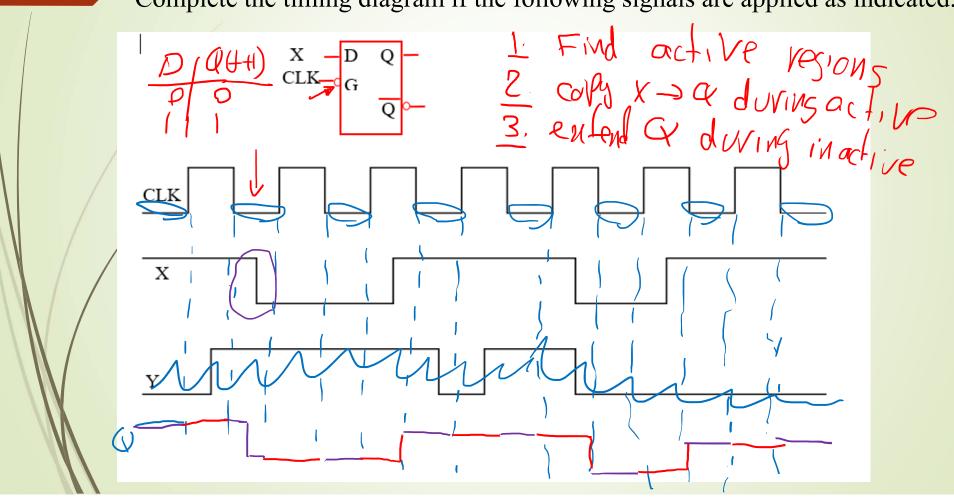

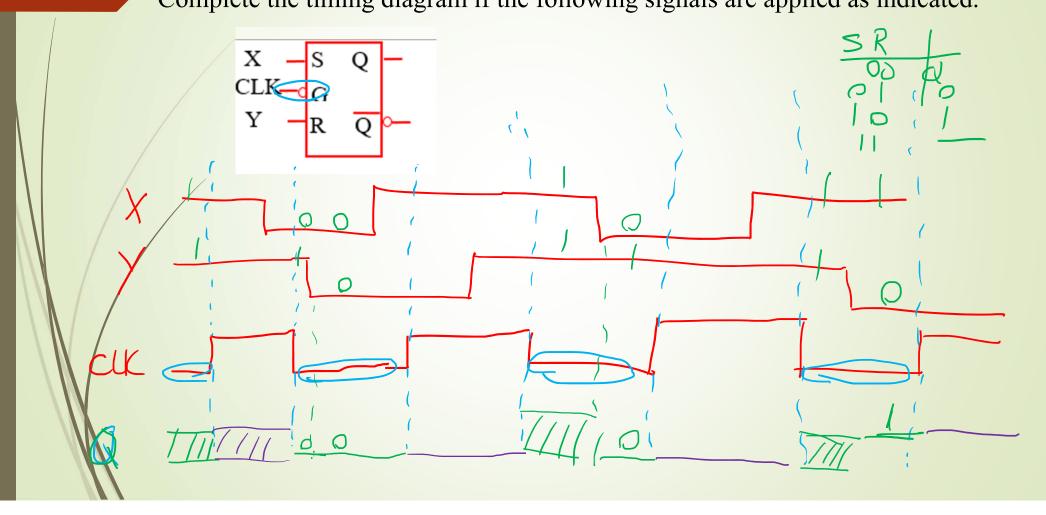

Complete the timing diagram if the following signals are applied as indicated.

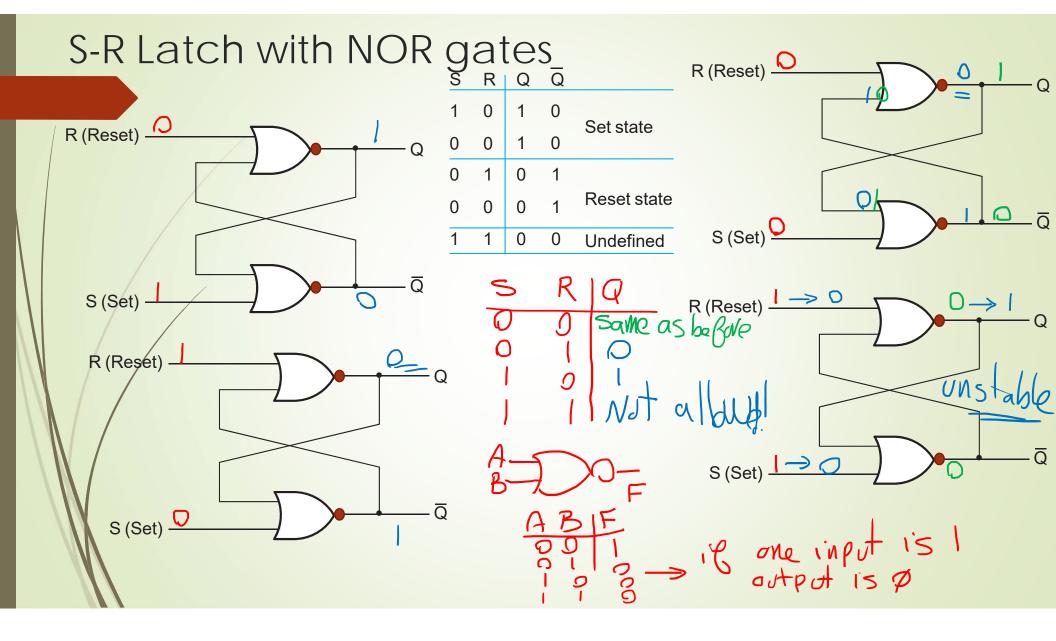

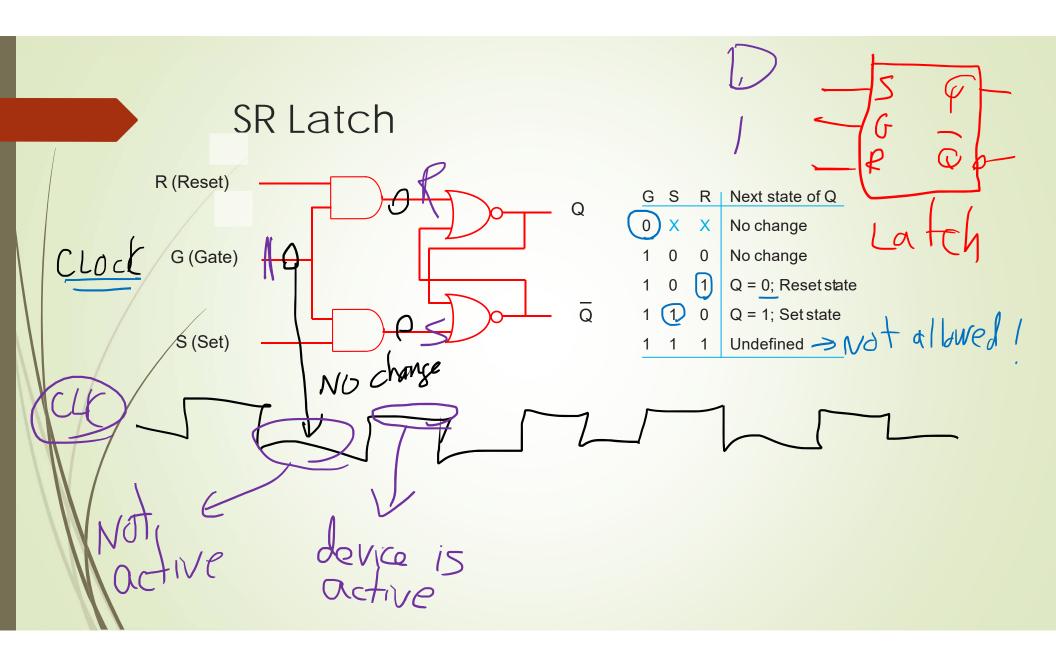

Problem 3

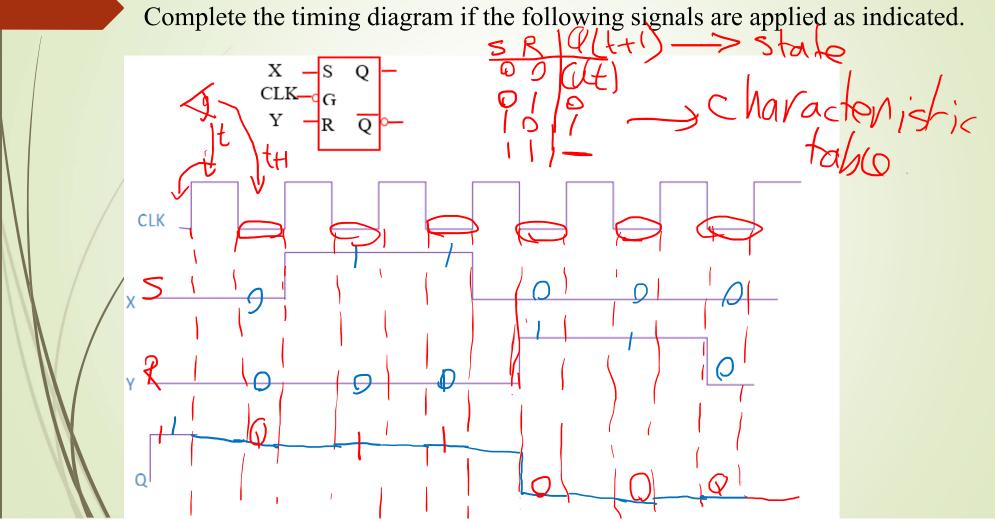

Complete the timing diagram if the following signals are applied as indicated.

Problem

Complete the timing diagram if the following signals are applied as indicated.

Problem 4

Complete the timing diagram if the following signals are applied as indicated.